# VINCHIP USB 3.0 CORE IP Super-Speed USB3.0 Device Controller

#### USB3.0 SuperSpeed Device

The Super Speed USB bus is implemented as a separate dual-simplex data path consisting of two uni-directional differential links, one for transferring data from the host downstream to peripherals and one for transferring data from peripherals upstream to the host. The D+/D- signal pins defined by USB 2.0 are not used for Super Speed operation but are provided to allow for backward compatible operation.

## Super-Speed USB Device Controller (VUSB30DC)

The Vinchip VUSB30DC core provides a USB functional device controller that conforms to the USB 3.0 specification for Super-Speed (5Gbps, 480 and 12 Mbps) functions. The core is user-configurable for up to 15 IN Endpoints and up to 15 OUT Endpoints in addition to Endpoint 0 (EP0). These additional Endpoints can be individually programmed for bulk/interrupt or isochronous transfers.

Each Endpoint requires an associated FIFO. The VUSB30DC has a RAM interface for connecting to a single block of synchronous dual-port RAM. The FIFO for Endpoint 0 is fixed at 64 bytes. The other Endpoint FIFOs may range upto the Maximum packet size of bytes in size and can buffer 1 or more packets. Separate FIFOs may be associated with each Endpoint.

#### **Major product features**

Complies with USB 3.0 standard for Super Speed(5.0 Gbps), Hi-Speed (480 Mbps) and Full-Speed (12 Mbps)

**VUSB30DC**

**PRODUCT BRIEF**

- Backward compatible with usb2.0 and the type A connectors.

- Technology and Process independent

- Data Interface is Dual-simplex, 4-wire differential signaling, separate from USB2.0 signaling.

- Supports Super speed UTMI transceiver interface with extension to the existing UTMI Interface for USB2.0

- Configurable up to 15 additional IN or OUT Endpoints

- Compatible USB transfer support for Control, Bulk, Interrupt and Isochronous transfers using USB3.0 Transaction/Handshake Packets and the Data Packets.

- Bus Transaction protocol is host directed and has asynchronous traffic flow. The packet traffic is explicitly routed.

- Parametrizable endpoint features for number, transfer type, direction of transfer, maximum packet size

- Built-in 32-bit synchronous AMBA AHBcompatible CPU interface

- Support for DMA access to FIFOs

- Synchronous Dual Port RAM interface for FIFOs

- Supports suspend and resume signaling

- Fully synthesizable

- Support all standard, Vendor specific control transfer requests

- Utility for core configuration of device descriptors and to wire endpoints.

#### Deliverables

- Verilog source code and test-bench

- scripts for simulation and synthesis

# VinChip Systems

# VINCHIP USB 3.0 CORE IP SUPER-SPEED USB3.0 DEVICE CONTROLLER

# VUSB30DC PRODUCT BRIEF

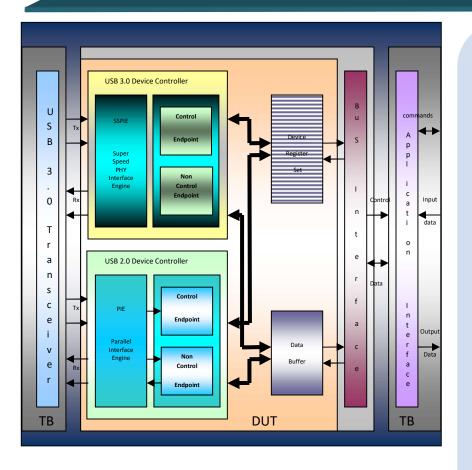

The VUSB30DC provides a USB 3.0 Transceiver Interface (UTMI extension to usb3.0) to connect to an Super-Speed transceiver. Access to the FIFOs and internal control/status registers may be via a 32-bit AMBA AHB-compatible synchronous CPU interface via the AMBA AHB bridge.

The VUSB30DC has a RAM interface for connecting to the single block of synchronous RAM that is used for all the Endpoint FIFOs. The device also offers support for DMA access to the Endpoint FIFOs. (The VUSB30DC-AHB bridge includes DMA controller hooks.)

This Super-Speed function controller provides the entire USB packet of encoding, decoding, and checking interrupting the CPU only when the Endpoint data has been successfully transferred.

An Utility is provided for configuring the core to the user's requirements.

This document describes its salient features and its internal organization below.

## **USB2.0** Device controller

This block contains the PIE (parallel interface engine), control endpoint and the non control endpoint controller blocks of the usb2.0 device. It interfaces to the backend bus through the endpoint RAM blocks and the device configuration registers.

**PIE** interface between the usb2.0 utmi phy interface and the device logical function endpoints.

**Control Endpoint** handles all the control transfers of the usb2.0 device including enumeration, standard and vendor specific requests.

**Non control Endpoint** controller handles bulk, ISO and interrupt transfer for the Backend application.

### **USB3.0** Device controller blocks

This block contains the SSPIE (Super Speed PHY Interface Engine, usb3 super speed control endpoint, usb3 super speed non-control endpoint blocks. In interfaces with the backend application through the USB3.0 Configuration Register set and the Endpoint RAM interface.

**SSPIE** interfaces between the usb3.0 super speed signals of the UTMI transceiver extension

**Control Endpoint** handles all the control transfers of the usb2.0 device including enumeration, standard and vendor specific requests.

Non control Endpoint controller handles bulk, ISO and interrupt transfer for the Backend application .

### **RAM Interface**

The RAM controller provides an interface to a dual-port synchronous RAM of size 16Kb, which is used to buffer packets between the MCU and the USB.

#### **Application Bus Interface**

Application interface block provides a seamless interface to popular processor buses. Variants are available to support 32-bit AMBA AHB compatible CPU, PCI and VCI. Supports DMA transfer type.

## **Products & Services**

VinChip's suite of soft cores for SoCs includes USB, WUSB, WiMedia Mboa Mac, PCI, AHB2PCI, SATA, Ethernet, PCI\_Express and Bluetooth controllers. These soft cores come with comprehensive documentation, verification environment, test suite, Drivers and tech support. Please contact us at info@vinchip.com for more information on our products and services.

> Copyright © 2008 VinChip Systems Inc. All rights reserved

Vinchip Systems, Inc 6020 Muldrow Rd, Carmichael, CA 95608, Ph: (408) 707-1420 Fax: (408) 243-2587 Email: info@vinchip.com\_www.vinchip.com

2