## VINCHIP USB 3.0 Core IP Super-Speed USB3.0 EXTENSIBLE HOST CONTROLLER (XHCI)

# VUSB30xHCI Product Brief

## USB3.0 Super-Speed Host

The Vinchip Super-Speed USB Host Controller is designed for flexibility, ease of use and provides ASIC/FPGA designers to implement a complete USB3.0 Host for 5 Gbps operation. The Host packet traffic can be explicitly routed and need not be broadcasted. The VUSB30xHC can be customized and optimized as a standalone host chip or integrated into ASIC for a variety of applications such as PCs, Smart phone's, etc. The D+/D- signal pins defined by USB 2.0 are not used for Super Speed operation but are provided to allow for backward compatible operation. The design is technology independent and can be easily processed in most technologies. It can be easily bridged to any industry standard bus including the PCI, PCI Express and AMBA AHB, AXI interfaces.

## Super-Speed USB3.0 Extensible Host Controller (VUSB30xHCI)

The Vinchip VUSB30xHC core provides a USB functional host controller that conforms to the USB 3.0 specification for Super-Speed (5 Gbps, 480 Mbps, 12 Mbps and 1.5 Mbps) functions. The xHC Host Controller has the flexibility to support USB2.0 and USB3.0 thus eliminating the need for the companion Host Controllers. It supports USB3.0 Power Management Enhancements and also enables USB Resource Management across VMs.

The extensible Host controller utilizes a common Host Buffer to initiate an USB Bus transaction for both Super-speed and USB2.0 devices. The RAM is used all kinds of USB transfers. The Bus interface unit handles the TRB transfer data storage with the Host buffers only through Bus Master DMA data transfers.

## **Major product features**

- Complies with USB 3.0 Standard for Super Speed (5 Gbps), High Speed (480 Mbps), Full-Speed (12 Mbps) and Low-Speed (1.5 Mbps).

- Complies with Intel xHCI specification for USB (revision 0.9).

- 32-bit addressing capability.

- Backward compatible with USB2.0 Devices and the type A connectors.

- Eliminates the need for companion host controllers along with its associated host software.

- Supports Bulk Streaming protocol and Data bursting.

- Supports Super speed USB PIPE and UTMI+ or ULPI transceiver interface.

- Supports USB3.0 Hub with simultaneous USB3.0 and 2.0 device transfers through the same hub. Also supports USB2.0 ping and USB2.0 Hub split transactions.

- Synchronous dual port scalable 2K RAM buffer separately for IN and OUT transfers.

- Compatible USB transfer support for Control, Bulk, Interrupt and Isochronous transfers using USB3.0 Transaction / Handshake Packets and the Data Packets.

- Technology and Process independent.

- Built-in 32-bit synchronous AMBA AHB-compatible CPU interface

- Integrated Root Hub and expandable downstream ports with support for all the USB bus speeds.

- Supports USB3.0 Power Management enhancements with suspend and resume.

- Fully synthesizable

- Utility for generation of ports expandability for the Host's downstream port.

## **Deliverables**

- Verilog source code and test-bench.

- Scripts for Simulation and key features

VinChip's USB 2.0 Host controller is designed for flexibility and ease of use and facilitates implementation of a wide variety of applications with fast turnaround time. This design is technology independent and migrating it to any technology is fast and simple. This EHC can be easily interfaced to standard buses such as ARM, S-Bus, etc

1

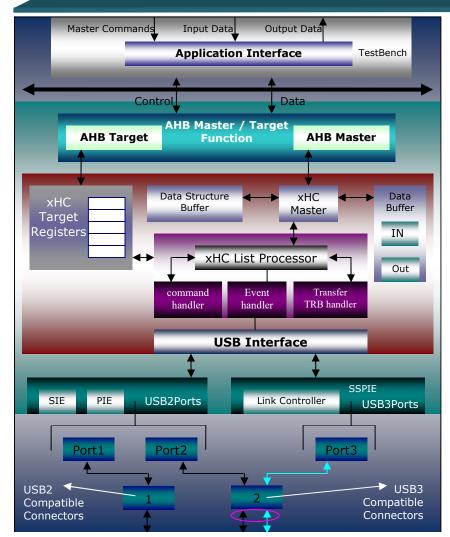

The VUSB30xHCI provides a USB 3.0 Host PIPE and UTMI+ or ULPI Transceiver Interface to connect to a Super-Speed USB transceiver. The AMBA AHB target interface provides access to the xHC internal control/status registers for a 32-bit AMBA AHB-compatible synchronous CPU through the AHB- bus bridge.

The VUSB30xHCI handles data transfers to/from the RAM (host buffers) through AHB Bus Master (DMA access) to transfer TRB data between the System Memory (Application software). The Vinchip xHCI Host controller for USB3.0 utilizes the host memory based transaction schedules.

This Super-Speed host controller provides the entire USB packet of encoding / decoding and also initiating Transaction packets (TP) and Data Packets (includes Data Packet Header (DPH) and Data Packet (DP)) through command TRBs, and notifies the host software with the USB events through event TRBs. USB3.0 also supports bulk streaming and burst transfers with sequence of ordered data packets, which can also recover the error packets during transfers.

A Utility is provided for parameterizing the downstream ports of the host core to the user's requirements.

This document describes its salient features and its internal organization below.

## **USB3.0 Host PHY Interface and Root Hub**

This block contains the SSDPIE (Superspeed Downstream PHY interface engine), HPIE (host parallel interface engine), HSIE (host serial Interface engine) and its root hub to handle the USB Devices. It interfaces to the xHC list processor through the USB interface block. The root hub block controls the USB downstream ports and also reports the port status information to the host software through the xHCI registers.

**SSDPIE** interfaces with the USB3.0 super speed signals of the USB3.0 PIPE transceiver interface.

**HPIE** interfaces between the USB2.0 UTMI+ PHY interface and the xHCI Host Controller block.

**HSIE** interfaces between the USB1.1 serial interface of the UTMI+ transceiver and the xHCI Host Controller block.

Root Hub handles downstream USB device connectivity, USB evVHDL / Verilog source code provided

#### **USB3.0 Extensible Host controller blocks**

This block contains the xHCI list processor which handles command TRB handling to initiate USB transactions, event TRBs to notify asynchronous information and transaction responses to the host software. The Transfer TRBs provide data source/sink for the data transfers to/from the USB devices.

**USB3.0 xHCI List Processor** handles all the processing of the command TRBs, to initiate transactions, handshake and data packets on the USB3.0 device including link layer management. It handles transaction responses and all USB asynchronous notifications to the host software through event TRBs. It also provides enhanced link power management support.

**USB3.0 xHCI Register Set, Data structure and Data Buffers** are responsible for controlling the USB host controller, providing status information and providing storage of host scheduled structures and USB data to handles USB transaction with the devices.

#### **RAM Interface**

The RAM controller provides an interface to a dual-port synchronous RAM of size 4Kb, which is used to buffer packets between the MCU and the USB. Separate IN and OUT RAM buffer of each 2K is provided for the USB data transfers.

#### **Application Bus Interface**

Application interface block provides a seamless interface to popular processor buses. Variants are available to support 32-bit AMBA AHB compatible CPU, PCI, PCI Express and VCI. Also, support DMA type of transfer.

## Products & Services

VinChip's suite of soft cores for SoCs includes USB, WUSB, WiMedia Mboa Mac, PCI, AHB2PCI, SATA, Ethernet, PCI\_Express and Bluetooth controllers. These soft cores come with comprehensive documentation, verification environment, test suite, Drivers and tech support. Please contact us at info@vinchip.com for more information on our products and services.

Copyright © 2008 VinChip Systems Inc. All rights reserved

Vinchip Systems, Inc 6020 Muldrow Rd, Carmichael, CA 95608, Ph: (408) 707-1420 Fax: (408) 243-2587 Email: info@vinchip.com\_www.vinchip.com